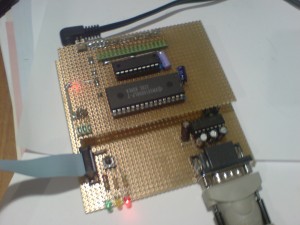

The Atmega8515 features a external memory interface that can be used to interface a external SRAM memory. The picture shows my Atmega8515 board with the

addon SRAM board. The small IC is a 74HC537 8-bit latch. The big one is a 128kByte SRAM memory. Only 64bit out of these can be addressed by the microcontroller. One thing that i found worth to notice is: The SRAM has two chip select inputs. The first is /CS1 and the second is CS2. The aim is to use one select signal (without inverter) to distinguish between two memories. I thought it is enougth to use one of the inputs and let the second floating. This was a mistake that caused me some hours of hunting a failure of sporadic instabilities during memory access. ;) The memory access is only valid if /CS1 is low and CS2 is high. I should read the datasheet before next time.

At the moment the whole application runs with a 12MHz crystal and without inserting wait-cycles during memory access. Hence i have a 74AC537 high speed latch i will try to go to 18.432MHz again. Above 14MHz it should be necessary to insert a wait cycle for read and write since the memory latency becomes to large. If one needs the speed he might use a cache memory instead.

Rauschfunk

V-U-SHF / SDR / DV and more by Mario, DH5YM